#### ABSTRACT OF THESIS

## HDL IMPLEMENTATION AND ANALYSIS OF A RESIDUAL REGISTER FOR A FLOATING-POINT ARITHMETIC UNIT

Processors used in lower-end scientific applications like graphic cards and video game consoles have IEEE single precision floating-point hardware [23]. Double precision offers higher precision at higher implementation cost and lower performance. The need for high precision computations in these applications is not enough to justify the use double precision hardware and the extra hardware complexity needed [23]. Native-pair arithmetic offers an interesting and feasible solution to this problem. This technique invented by T. J. Dekker uses single-length floating-point numbers to represent higher precision floating-point numbers [3]. Native-pair arithmetic has been proposed by Dr. William R. Dieter and Dr. Henry G. Dietz to achieve better accuracy using standard IEEE single precision floating point hardware [1]. Native-pair arithmetic results in better accuracy however it decreases the performance by 11x and 17x for addition and multiplication respectively [2]. The proposed implementation uses a *residual register to* store the error residual term [2]. This addition is not only cost efficient but also results in acceptable accuracy with 10 times the performance of 64-bit hardware. This thesis demonstrates the implementation of a 32-bit floating-point unit with residual register and estimates the hardware cost and performance.

Keywords: Native-pair floating-point unit residual VHDL

## HDL IMPLEMENTATION AND ANALYSIS OF A RESIDUAL REGISTER FOR A FLOATING-POINT ARITHMETIC UNIT

ΒY

Akil Kaveti

Dr. William R. Dieter

**Director of Thesis**

Dr. YuMing Zhang

Director of Graduate Studies

March 25, 2008

#### Rules for the use of theses

Unpublished theses submitted for the Master's degree and deposited in the University of Kentucky Library are as a rule open for inspection, but are to be used only with due regard to rights of the authors. Bibliographical references may be noted, but quotations or summaries of parts may be published only with the permission of the author, and with the usual scholarly acknowledgements.

Extensive copying or publication of the thesis in whole or in part also requires the consent of the Dean of the Graduate School of the University of Kentucky.

A Library that borrows this thesis for use by its patrons is expected to secure the signature of each user.

Name

Date

THESIS

Akil Kaveti

The Graduate School University Of Kentucky 2008

### HDL IMPLEMENTATION AND ANALYSIS OF A RESIDUAL REGISTER FOR A FLOATING-POINT ARITHMETIC UNIT

#### MASTERS THESIS

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering at the University of Kentucky

By

Akil Kaveti

Lexington, Kentucky

Director of Thesis: Dr. William Dieter

Electrical Engineering, University of Kentucky,

Lexington, Kentucky

2008

Copyright <sup>©</sup> Akil Kaveti 2008

#### ACKNOWLEDGEMENTS

Foremost I would like to thank my advisor, Dr. William R. Dieter for providing me the opportunity to do this thesis. I am grateful to him for his constant guidance and support. I would also like to thank Dr. Hank Dietz for his suggestions which have helped in improving this thesis.

I would like to thank my Candy for being such a wonderful person and for motivating me time and again.

Most importantly I would like to thank my parents for their love and support I dedicate my thesis to them.

## **Table of Contents**

| ACKNOWLEDGEMENTS                                       | iii  |

|--------------------------------------------------------|------|

| Table of Contents                                      | iv   |

| List of Figures                                        | vi   |

| List of Tables                                         | vii  |

| List of Files                                          | viii |

| Chapter 1. Introduction                                | 1    |

| 1.1. Computer Representation of Real Numbers           | 1    |

| 1.2. Hardware Assistance of Native-Pair                |      |

| 1.3. Thesis Organization                               | 4    |

| Chapter 2. Background                                  | 6    |

| 2.1. IEEE 754 Floating-point standard                  | 6    |

| 2.2. IEEE 754 Floating-point Arithmetic                |      |

| 2.3. History of Double-Double Arithmetic               |      |

| 2.4. The Residual Register                             |      |

| 2.5. Native-pair Addition and Subtraction              |      |

| 2.6. Native-pair Multiplication                        |      |

| Chapter 3. Native-pair Floating-point Unit             |      |

| 3.1. Native Floating-Point Addition/Subtraction        |      |

| 3.2. Native Floating-Point Multiplication              |      |

| 3.3. Native-pair Floating-point Addition/subtraction   |      |

| 3.4. Native-pair Floating-point Multiplication         |      |

| 3.5. Debugging FPU Unit                                |      |

| 3.6. Examples                                          | 50   |

| Chapter 4. Testing and Results                         |      |

| Chapter 5. Estimation of Hardware Cost and Performance | 71   |

| 5.1. Adder Implementation                              | 71   |

| 5.2. Multiplier Implementation                         | 73   |

| Conclusion                                             | 76   |

| Appendix A             |    |

|------------------------|----|

| Post-route simulations |    |

| Appendix B             |    |

| High-level Schematics  | 83 |

| VHDL Source Code       |    |

| References             |    |

| Vita                   |    |

## List of Figures

| Figure 1. Number line showing the ranges of single-precision denormalized and              |

|--------------------------------------------------------------------------------------------|

| normalized floating-point numbers in binary system.                                        |

| Figure 2. Ranges of overflow and underflow for single-precision floating-point numbers     |

|                                                                                            |

| Figure 3. Basic floating-point addition algorithm                                          |

| Figure 4. Basic Floating-point multiplication algorithm                                    |

| Figure 5. Residual register                                                                |

| Figure 6. Native-pair addition data flow, conventional and residual algorithms             |

| Figure 7. Native-pair multiplication data flow, conventional and residual algorithms 29    |

| Figure 8. Prenormalization unit for Floating-point addition                                |

| Figure 9. Addition unit for Floating-point addition                                        |

| Figure 10. Postnormalization unit for Floating-point addition                              |

| Figure 11. Prenormalization unit in floating-point multiplication                          |

| Figure 12. Multiplication unit for Floating-point multiplication                           |

| Figure 13. Postnormalization unit for Floating-point multiplication                        |

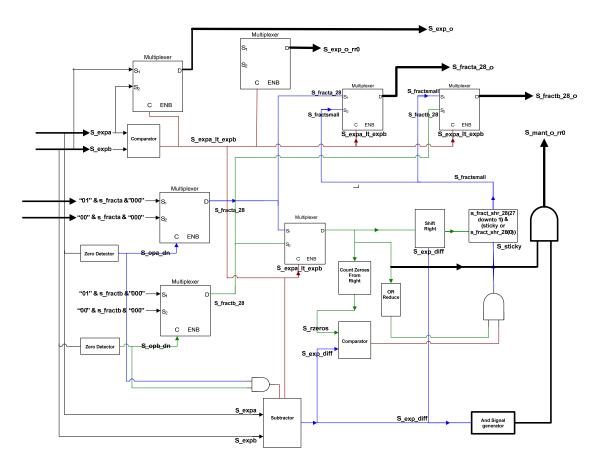

| Figure 14. Prenormalization unit for Native-pair Addition using Residual register 38       |

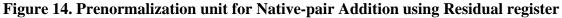

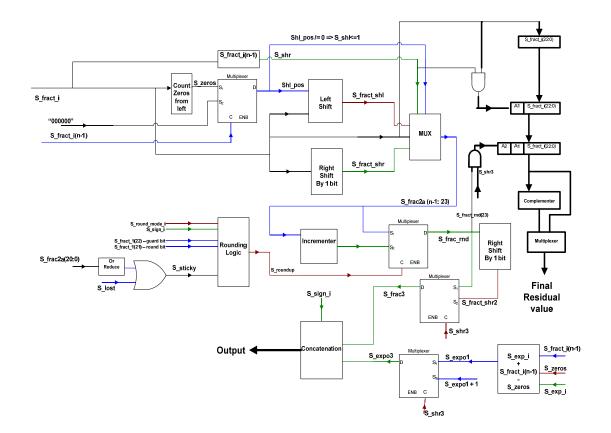

| Figure 15. Postnormalization unit for Native-pair addition with Residual register 41       |

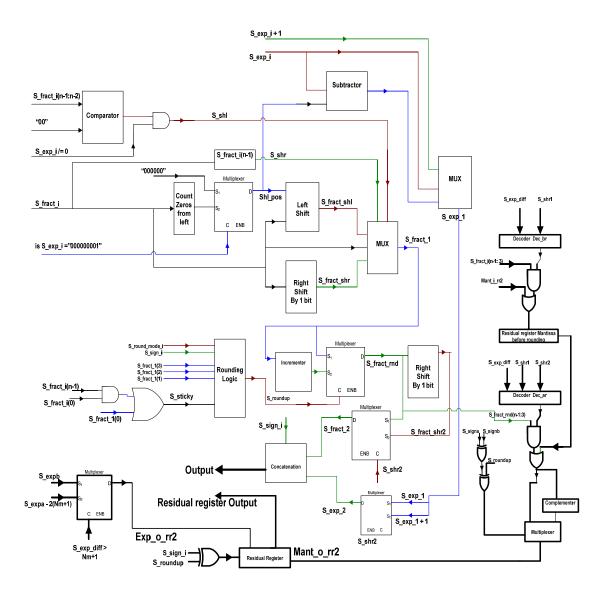

| Figure 16. Postnormalization unit for Native-pair multiplication with Residual register 43 |

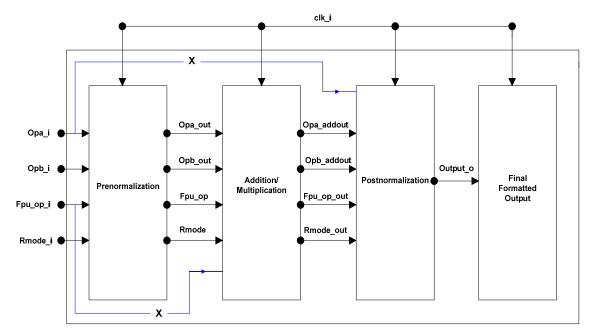

| Figure 17. Floating point arithmetic unit pipeline 46                                      |

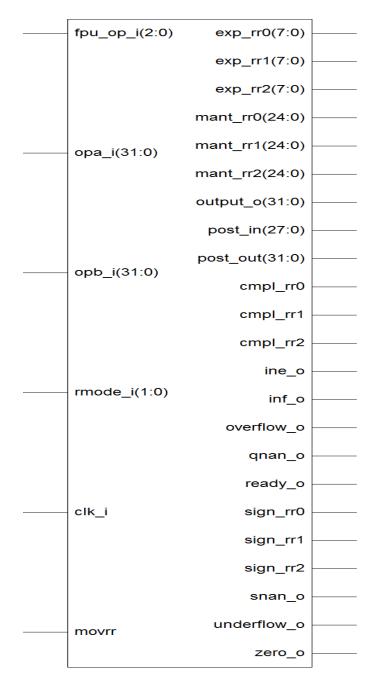

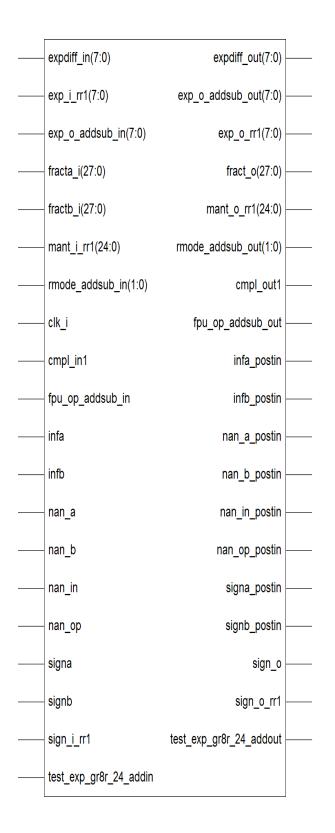

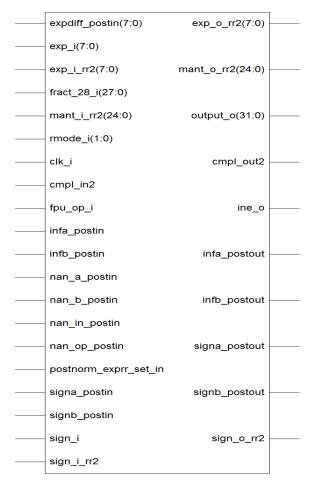

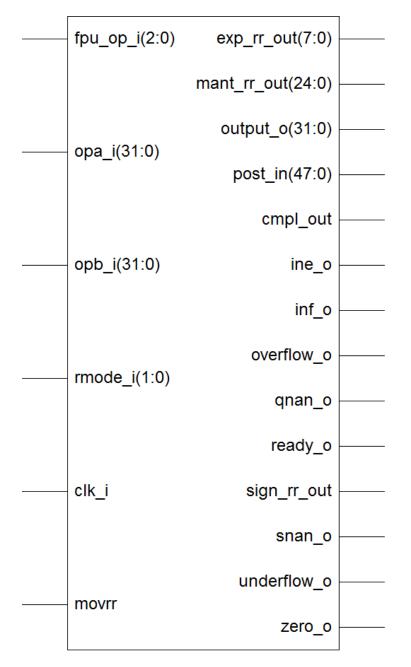

| Figure 18: High-level schematic of FPU Adder                                               |

| Figure 19. High-level schematic Prenormalization unit used in Floating-point addition.84   |

| Figure 20. High-level schematic of Addition unit used in Floating-point addition           |

| Figure 21. High-level schematic of Postnormalization Unit used in Floating-point           |

| addition                                                                                   |

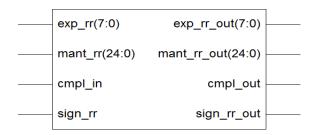

| Figure 22. High-level schematic of Residual register used in prenormalization and          |

| postnormalization                                                                          |

| Figure 23. High-level schematic of FPU multiplier                                          |

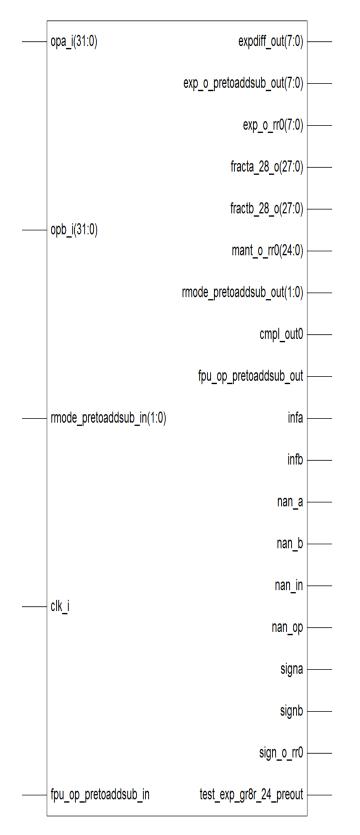

| Figure 24. High-level schematic of Prenormalization unit for Multiplier                    |

| Figure 25. High-level schematic of Multiplier unit                                         |

| Figure 26. High-level schematic of Postnormalization for Multiplier                        |

## List of Tables

| Table 1. Layouts for single and double precision numbers in IEEE 754 format               |

|-------------------------------------------------------------------------------------------|

| Table 2. Representation of single-precision binary floating-point numbers                 |

| Table 3. Different cases for sign and complement flag of residual register                |

| Table 4. Cases for complement flags and signs of residual register                        |

| Table 5. Addition or subtraction cases based on opcode and signs of the operands 33       |

| Table 6. Comparison of Implementation cost and delay for Adders                           |

| Table 7. Comparison of device utilization reports of Prenormalization unit for 32-bit FPU |

| adder with and without residual register hardware72                                       |

| Table 8. Comparison of device utilization reports of Postnormalization unit for 32-bit    |

| FPU adder with and without residual register hardware                                     |

| Table 9. Comparison of Implementation cost and delay of Multipliers                       |

| Table 10. Comparison of device utilization reports of Postnormalization unit for 32-bit   |

| FPU multiplier with and without residual register hardware                                |

## List of Files

| Name of figure                                                                             | Туре | Size<br>(KB) | Page |

|--------------------------------------------------------------------------------------------|------|--------------|------|

| Figure 6. Native-pair addition data flow, conventional and residual algorithms.            | .vsd | 50           | 25   |

| Figure 7. Native-pair multiplication data flow, conventional and residual algorithms.      | .vsd | 60           | 29   |

| Figure 8. Prenormalization unit for Floating-point addition                                | .vsd | 114          | 31   |

| Figure 9. Addition unit for Floating-point addition                                        | .vsd | 96           | 32   |

| Figure 10. Postnormalization unit for Floating-point addition.                             | .vsd | 107          | 34   |

| Figure 11. Prenormalization unit in floating-point multiplication                          | .vsd | 85           | 35   |

| Figure 12. Multiplication unit for Floating-point multiplication                           | .vsd | 50           | 36   |

| Figure 13. Postnormalization unit for Floating-point multiplication                        | .vsd | 113          | 37   |

| Figure 14. Prenormalization unit for Native-pair Addition using<br>Residual register       | .vsd | 122          | 38   |

| Figure 15. Postnormalization unit for Native-pair addition with Residual register          | .vsd | 152          | 41   |

| Figure 16. Postnormalization unit for Native-pair multiplication<br>with Residual register | .vsd | 113          | 43   |

| Figure 17. Floating point arithmetic unit pipeline                                         | .vsd | 64           | 46   |

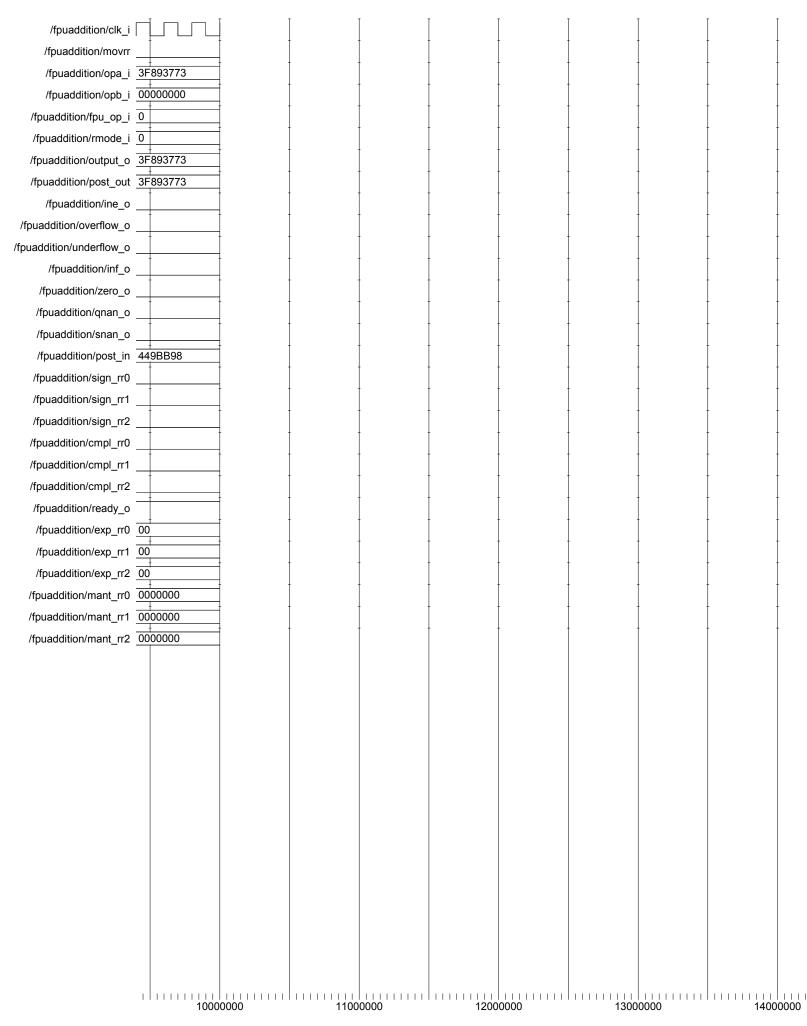

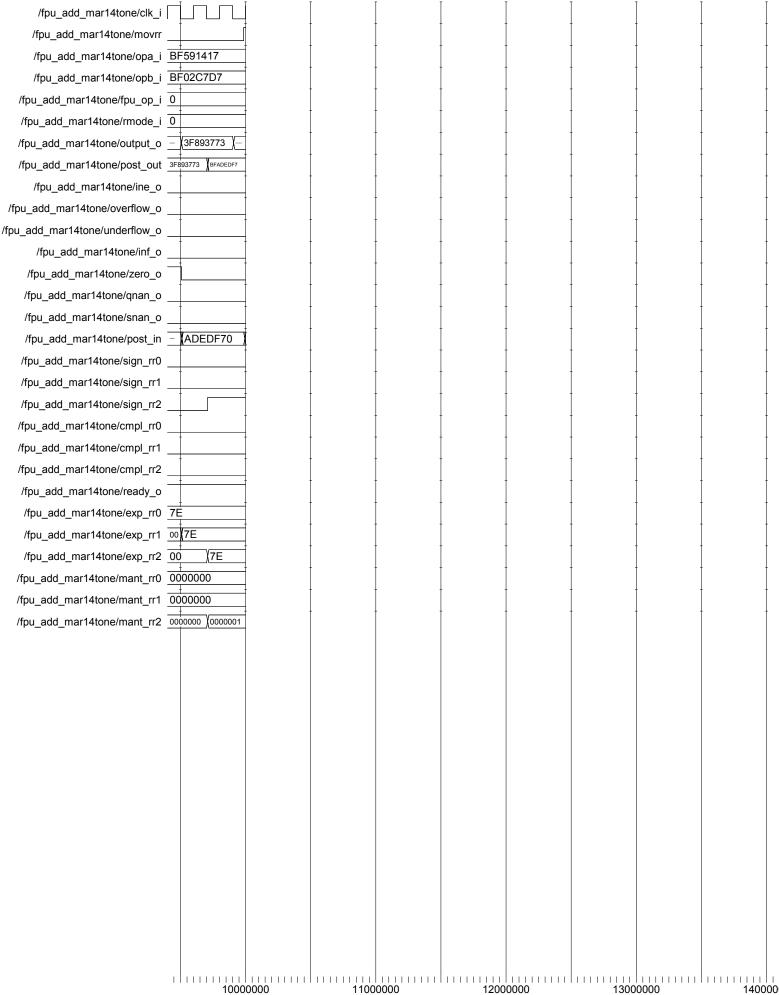

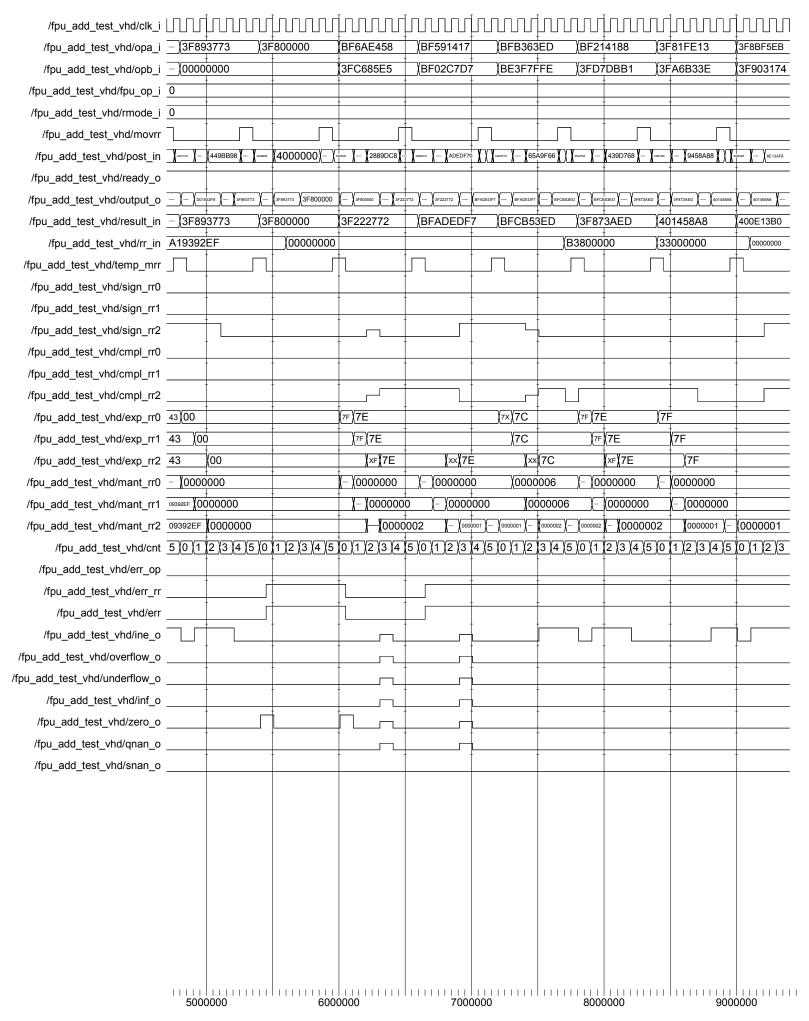

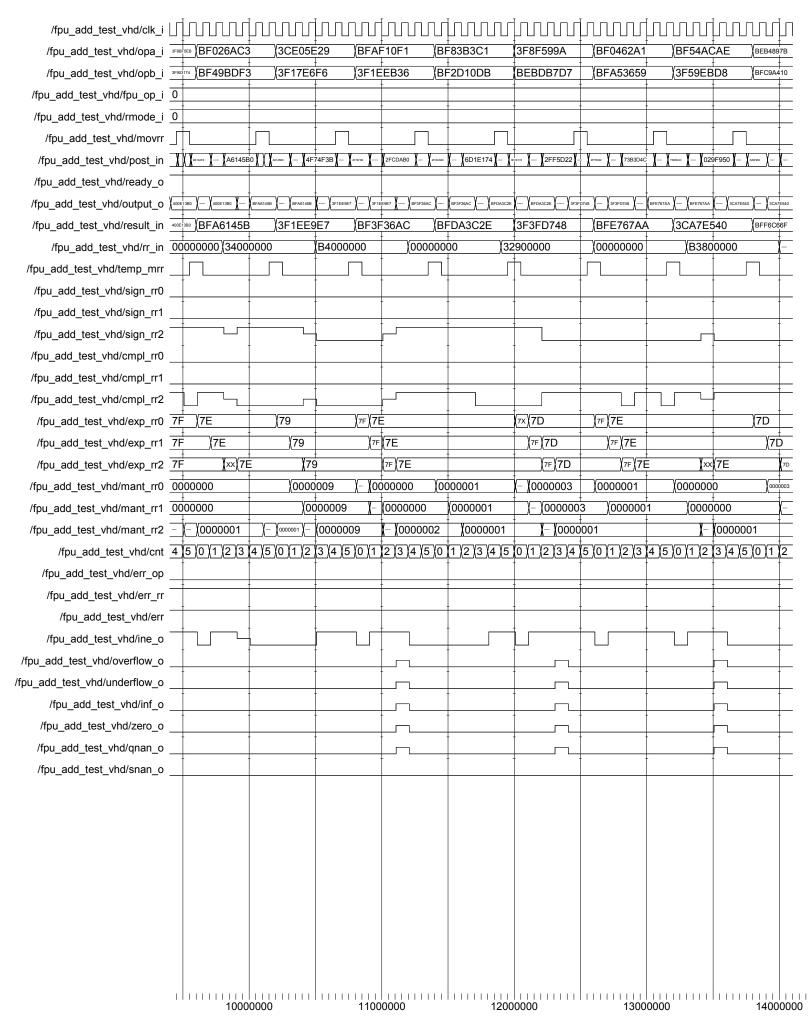

| Addition testbenchwave                                                                     | .pdf | 130          | 90   |

| Additionwave1                                                                              | .pdf | 71           | 93   |

| Additionwave2                                                                              | .pdf | 69           | 97   |

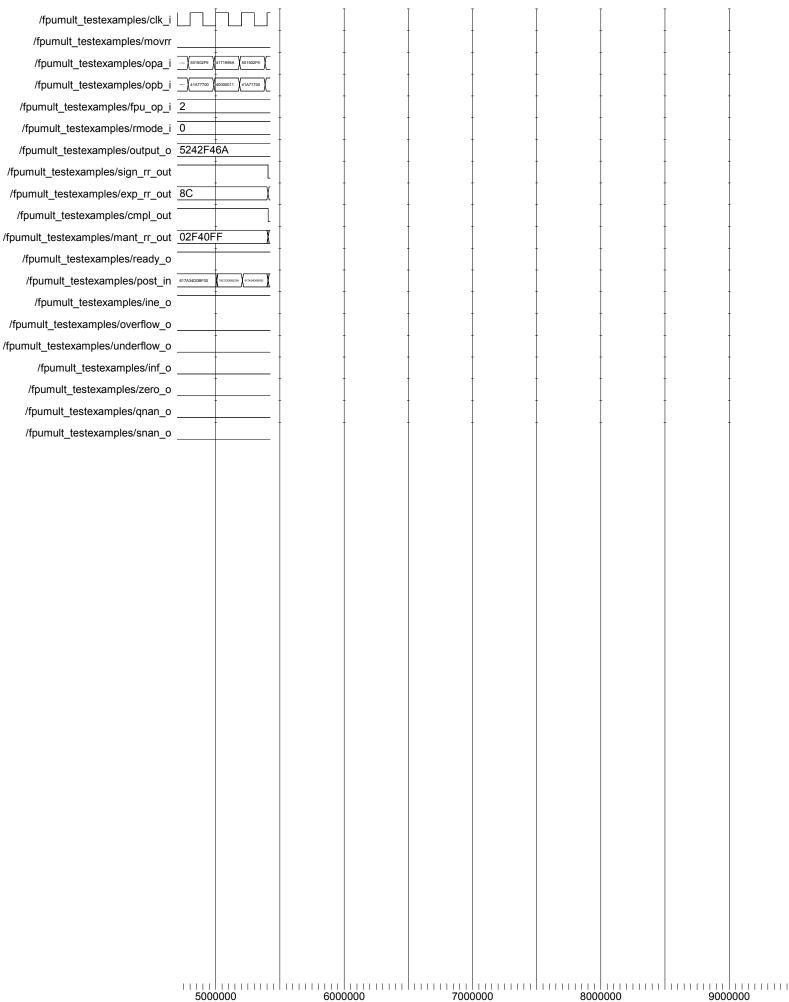

| Fpumultfinal1                                                                              | .pdf | 32           | 103  |

| Fpumultfinal2                                                                              | .pdf | 44           | 104  |

#### **Chapter 1. Introduction**

This chapter briefly introduces all the topics that will be encountered and described in the later parts of the thesis. It starts by giving the reason for using floating-point numbers in computation. It discusses the floating-point arithmetic, cost involved in implementing higher precision than the existing floating-point hardware, native-pair arithmetic and its usage for better precision and accuracy, performance-cost factor in native-pair arithmetic and extra hardware support to improve the performance-cost factor. This chapter ends with the author's motivation to work on native-pair Floating-point Arithmetic unit and the organization of the thesis.

#### **1.1. Computer Representation of Real Numbers**

Real numbers may be described as numbers that can represent a number with infinite precision and are used to measure continuous quantities. Almost all computations in Physics, Chemistry, Mathematics or scientific computations, all involve operations using real numbers. Computers can only approximate real numbers, most commonly represented as fixed-point and floating-point numbers. In a Fixed-point representation, a real number is represented by a fixed number of digits before and after the radix point. Since the radix point is fixed, the range of fixed-point also is limited. Due to this fixed window of representation, it can represent very small numbers or very large numbers accurately within the available range. A better way of representing real numbers is floating-point representation. Floating-point numbers represent real numbers in scientific notation. They employ a sort of a sliding window of precision or number of digits suitable to the scale of a particular number and hence can represent of a much wider range of values accurately. Floating-point representation has a complex encoding scheme with three basic components: mantissa, exponent and sign. Usage of binary numeration and powers of 2 resulted in floating point numbers being represented as single precision (32-bit) and double precision (64-bit) floating point numbers. Both single and double precision numbers are defined by the IEEE 754 standard. According to the standard, a single precision number has one sign bit, 8 exponent bits and 23 mantissa bits where as a double precision number comprises of one sign bit, 11 exponent bits and 52 mantissa bits.

Most processors designed for consumer applications, such as Graphical Processing Units (GPUs) and CELL processors promise and deliver outstanding floating point performance for scientific applications while using the single precision floating point arithmetic hardware [23][6]. Video games rarely require higher accuracy in floating-point operations, the high cost of extra hardware needed in their implementation is not justified. The hardware cost of a higher precision arithmetic is lot greater than singleprecision arithmetic. For example, one double precision or 64-bit floating point pipeline has approximately same cost as two to four 32-bit floating-point pipelines [1]. Most applications use 64-bit floating point to avoid losing precision in a long sequence of operations used in the computation, even though the final result may not be accurate to more than 32-bit precision. The extra precision is used so the application developer does not have to worry about having enough precision. Native-pair arithmetic presents an opportunity to increase the accuracy of a single-precision or 32-bit floating-point arithmetic without incurring the high expense of a double-precision or 64-bit floatingpoint arithmetic implementation. Native-pair arithmetic uses two native floating-point numbers to represent the base result and the resulting error residual term that would have been discarded in a native floating point unit [23]. One native floating-point number is represented using two native floating-point numbers. This approach has been adapted from an earlier technique known as double-double arithmetic. Double-double arithmetic is the special case of native-pair arithmetic using two 64-bit double precision floating point numbers to represent one variable; the first floating-point number representing the leading digits and the second the trailing digits [17]. Similarly in Native-pair arithmetic, two 32-bit floating-point numbers are used to represent high and low terms where low component encodes the residual error from high component representation. Though this implementation results in higher accuracy without external hardware, it also degrades in performance [2].

#### 1.2. Hardware Assistance of Native-Pair

In order to obtain acceptable accuracy with less performance loss, addition of simple micro-architectural hardware is needed. Dieter and Dietz proposed a residual register to hold discarded information after each floating-point computation [2]. This feature not only reduces the performance cost of native-pair arithmetic but also provides lower latency and better instruction-level parallelism. A residual register has one sign bit, 8 exponent bits and 25 mantissa bits [23]. The usage of the residual register depends on what operation is being performed and at what stage or stages are the bits being discarded.

The most widely used floating-point standard is the IEEE 754 standard. The IEEE 754 standard prescribes a particular format for representing floating-point numbers in binary system, special floating-point numbers, rounding modes, exceptions and how to handle them. Floating-point operations such as addition, multiplication, division and square root have three stages viz., prenormalization, arithmetic unit and postnormalization. In the case of addition and subtraction, prenormalization increases or decreases the exponent part to align the mantissa parts, calculates the sign bit of the final result. The arithmetic unit does the basic arithmetic involving the mantissa bits. The result may not be in the appropriate format, so it is sent into the postnormalization unit. It is in the postnormalization that the result from previous stage is aligned to the IEEE 754 format, rounded depending on the rounding mode and the number with its sign, exponent and mantissa bits is given as the final result.

This thesis aims to prove that residual register hardware with minimal increase in hardware cost results in accuracy close to double-precision and hence is the more economically feasible solution for higher precision arithmetic than the double-precision hardware. Native-pair arithmetic presents an opportunity for more accurate and precise floating-point processing, but it also results in a decrease in performance and increase in implementation cost when compared with the single precision or 32-bit floating-point hardware [23]. The usage of residual register as the extra hardware for storing the error

residual term in native-pair arithmetic gives an implementation which has a slight increase in hardware cost coupled with performance close to that of single precision hardware [23]. Floating point arithmetic unit with residual register is implemented and its hardware utilization, maximum operable frequency is compared with the 32-bit and 64-bit floating-point arithmetic unit implementations. The main idea is to find the extra hardware cost and the performance drop resulting due to the residual register usage, moving the discarded bits into it, updating the residual register if bits are discarded more than once and also setting the sign and exponent of the residual register. The implemented floating-point unit uses the residual register with addition, subtraction and multiplication. The extra hardware needed accounted to an increase of 18% in adder and 12% in multiplier. A minimum period increase of 19% for adder and 12% for multiplier also resulted due to addition of extra hardware in the critical path. The divide and the square root portions of the floating-point unit are left unchanged.

A floating-point unit coded in VHDL was adopted for the purpose of developing a Native-pair Floating point unit from it [19]. The initial part of this thesis was to debug the code and make it fully pipelined to generate outputs on continuous clock cycles. Signals were added to carry the input operands and the intermediate outputs through the pipeline to wherever needed. Those signals which were present in the final stages and required input operands to be set have been moved to starting stage in order to eliminate the need to carry input operands. The Native-pair floating point unit is implemented by adding the residual register hardware to the debugged native floating point unit. The debugged code is a single precision or 32-bit floating point unit and was scaled to serve as a 64-bit floating point unit. The synthesis reports for the three implementations viz., 32-bit version, native-pair version or 32-bit with residual register and 64-bit version were obtained using Xilinx 9.1 ISE tool and a comparison of their resource utilizations and minimum periods is obtained.

#### 1.3. Thesis Organization

In Chapter 2 forms the background of this thesis. It discusses in detail the IEEE 754 floating-point arithmetic standard, IEEE 754 floating-point addition/subtraction, multiplication, Native-pair arithmetic, Native-pair arithmetic algorithms. Chapter 3

describes the working of 32-bit floating-point unit and native-pair floating-point unit with residual register. The different components of a floating-point unit are discussed in this chapter. Also covered in this chapter is where the residual register is added, how it is set or updated, when it is complemented and how its sign is set, usage of the MOVRR instruction. Chapter 4 describes how the Native-pair floating-point unit is tested. This chapter covers the test- benches used to test the implementation. Chapter 5 consists of the post map and route simulation reports, synthesis reports of native-pair floating point unit, 32-bit floating point unit and 64-bit floating point unit.

Chapter 6 compares the synthesis reports, provides a more detailed analysis of the implementation. Chapter 7 concludes the thesis and discusses the avenue for future research.

#### Chapter 2. Background

Hardware supporting different floating-point precisions and various formats have been adopted over the years. Amongst the earliest programmable and fully automatic computing machines, the Z3 built of relays and performed calculations using 22-bit word lengths in binary floating-point arithmetic [21]. The first commercial computer supporting floating-point, the Z4, had floating point hardware that supported 32-bit word length comprising of 7 bit exponent, 1 sign bit and 24 mantissa bits [22]. The second one was the IBM 704 in 1954 whose floating point hardware supported a format consisting of 1 sign bit, 8-bit exponent and 29-bit magnitude. IBM considered the 704 format as single precision and later in the IBM 7094 double precision was introduced which had a sign bit, 17-bit exponent and 54-bit magnitude [20]. The DEC – Digital Equipment Corporation's PDP 11/45 had an optional floating point processor. This processor is considered a predecessor to the IEEE 754 standard as it had a similar single precision format. The NorthStar FPB-A was a S100 bus floating point microprogram controlled processor, built on medium and small scale TTL parts and PROM memories to perform high speed decimal floating point arithmetic operations. It supported 2, 4, 6, 8, 10, 12, 14 digit precision and 7-bit base-10 exponent [25] [23]. The MASPAR MP1 supercomputer performed floating point operations using 4-bit slice operations on the mantissa with special normalization hardware and supported 32-bit and 64-bit IEEE 754 formats.

The CELL processor, most DSPs and GPUs support the IEEE 32-bit format. The Intel X87 floating point mechanism allows 32-bit, 64-bit and 80-bit operands but processes these operands using an 80-bit pipeline [23] [6] [7]. The standardization of IEEE 754 floating point standard in 1985 has greatly improved the portability of floating-point programs. This standard has been widely accepted and is used by most processors built since 1985.

#### 2.1. IEEE 754 Floating-point standard

The IEEE 754 floating-point standard is the most widely used standard for floating-point computations and is followed in most of the CPU and FPU (Floating point unit) implementations. The standard defines a format for floating-point numbers, special

numbers such as the infinite's and NAN's, a set of floating-point operations, the rounding modes and five exceptions. IEEE 754 specifies four formats of representation: single-precision (32-bit), double-precision (64-bit), single extended ( $\geq$  43 bits) and double extended precisions ( $\geq$  79 bits).

Under this standard, the floating point numbers have three components: a sign, an exponent and a mantissa. The mantissa has an implicit hidden leading hidden bit and the rest are fraction bits. The most used formats described by this standard are the single-precision and the double-precision floating-point number formats which are shown in Table 1. In each cell the first number indicates the number of bits used to represent each component, and the numbers in square brackets specify bit positions reserved for each component in the single-precision and double-precision numbers.

| Format           | Sign   | Exponent     | Fraction / Mantissa | Bias |

|------------------|--------|--------------|---------------------|------|

| Single-precision | 1 [31] | 8 [30 – 23]  | 23 [22 – 0]         | 127  |

| Double-precision | 1[63]  | 11 [62 - 52] | 52 [51 - 0]         | 1023 |

Table 1. Layouts for single and double precision numbers in IEEE 754 format.

The Sign bit: A sign bit value of 0 is used to represent positive numbers and 1 is used to represent negative numbers

The Exponent: The exponent field has 8 bits in single-precision and 11 bits in doubleprecision. The value is stored in unsigned format and a *bias* is added to the actual exponent to get the stored exponent. For single-precision, the bias value is 127 and for double-precision it is 1023. Actual exponent = stored exponent – 127 for single-precision and it is equal to stored exponent – 1023 for double-precision. Denormalized numbers and zero have all zeroes in the exponent field. The infinite and Not a number values have all one's in the exponent field. The range of the exponent for single precision is from -126 to +127 and for double-precision it is -1022 to +1023.

The Mantissa: Apart from the sign and the exponent a floating-point number also has a magnitude part which is represented by the mantissa field. For single-precision the

number of mantissa bits is 23 and for double-precision it is 52. Each mantissa has a hidden bit which is not shown when the floating-point is represented in the IEEE format. This is because all the floating-point numbers are adjusted to have this hidden bit equal to 1 and so the fact that hidden bit is 1 is understood and so is not specified explicitly. Denormalized numbers have the hidden bit set to zero.

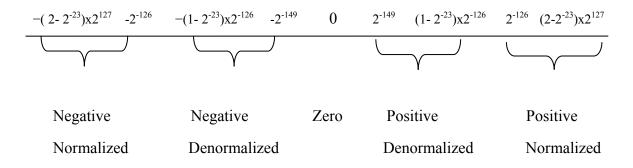

In general, floating-point numbers are stored in normalized form. This puts the radix point after the first non-zero digit. In normalized form, six is represented as  $+ 6.0 \times 10^{0}$ . In binary floating-point number representation, the radix point is placed after a leading 1. In this form six is represented as  $+ 1.10 \times 2^{2}$ . In general, a normalized floating-point number is represented as  $\pm 1. f \times 2^{e}$ . There is an implicit leading hidden 1 before the radix point and 23 visible bits after the radix point. The value of the IEEE 754 32-bit floating point number can be computed from the sign bit (s), 8-bit biased exponent field (e), and 23-bit fraction field (f) and arranging them as follows: Value =  $(-1)^{s} 2^{e-127} \times 1.f$

When a nonzero number is being normalized, the mantissa is shifted left or right. Each time a left shift is performed, the exponent is decremented. In case the minimum exponent is reached but further reduction is still required, then the exponent value is taken 0 after biasing, such a number is a denormalized number. Hence a number having zeroes in its exponent field and at least a single 1 in its mantissa part is said to be a denormalized number. The IEEE 754 standard represents the denormalized number as follows: Value =  $(-1)^{s} 2^{-126} \times 0.6$

Figure 1. Number line showing the ranges of single-precision denormalized and normalized floating-point numbers in binary system.

| Sign | Exponent | Mantissa                                | Value                         |

|------|----------|-----------------------------------------|-------------------------------|

| 0    | 00000000 | 000000000000000000000000000000000000000 | + 0                           |

| 1    | 00000000 | 000000000000000000000000000000000000000 | -0                            |

| 0    | 11111111 | 000000000000000000000000000000000000000 | $\infty +$                    |

| 1    | 11111111 | 000000000000000000000000000000000000000 | -∞-                           |

| 0    | 00000000 | 000000000000000000000000000000000000000 | Positive Denormalized         |

|      |          |                                         | floating-point numbers        |

|      |          | to                                      |                               |

|      |          |                                         |                               |

|      |          | 111111111111111111111111111111111111111 |                               |

| 1    | 00000000 | 000000000000000000000000000000000000000 | Negative Denormalized         |

|      |          |                                         | floating-point numbers        |

|      |          | to                                      |                               |

|      |          |                                         |                               |

|      |          | 111111111111111111111111111111111111111 |                               |

| 0    | 00000001 | ******                                  | Positive Normalized floating- |

|      |          |                                         | point numbers                 |

|      | to       |                                         |                               |

|      | 11111110 |                                         |                               |

| 1    | 00000001 |                                         | Negative Normalized floating- |

| 1    | 0000001  |                                         | point numbers                 |

|      | to       |                                         | point numbers                 |

|      | 10       |                                         |                               |

|      | 11111110 |                                         |                               |

| 0/1  | 11111111 | 100000000000000000000000000000000000000 | QNaN - Quiet Not a Number     |

|      |          |                                         |                               |

|      |          | to                                      |                               |

|      |          |                                         |                               |

|      |          | 111111111111111111111111111111111111111 |                               |

| 0/1  | 11111111 | 000000000000000000000000000000000000000 | SNaN – Signaling Not a        |

|      |          |                                         | Number                        |

|      |          | То                                      |                               |

|      |          |                                         |                               |

|      |          | 011111111111111111111111111111111111111 |                               |

Table 2. Representation of single-precision binary floating-point numbers

## Exceptions

IEEE 754 floating-point standard defines five exceptions that are generally signaled using a separate flag. They are as follows:

Invalid Operation: Some operations like divide by zero, square root of a negative number or addition and subtraction from infinite values are invalid. The result of such invalid operation is NaN – Not a Number. NaNs are of two types: QNaNs, or Quiet NaNs, and SNaNs or signaling NaNs. Their formats are shown in table 2.

The result of an invalid operation will result be a QNaN with a QNaN or SNaN exception. The SNaN can never be the result of any operation, only its exception can be signaled and this happens whenever one of the operands to a floating-point operation is SNaN. The SNaN exception can be used to signal operations with uninitialized operands, if we set the uninitialized operands to SNaN. The usage of SNaN is not subject to the IEEE 754 standard.

- 2. Inexact: This exception is signaled when the result of an arithmetic operation cannot be represented due to restricted exponent range or mantissa precision

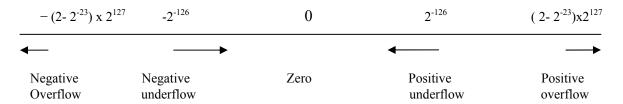

- 3. Underflow: Two events cause that underflow exception to be signaled are tininess and loss of accuracy. Tininess is detected after or before rounding when a result lies between  $\pm 2^{-126}$ . Loss of accuracy is detected when the result is simply inexact or only when a denormalization loss occurs.

- 4. Overflow: The overflow exception is signaled whenever the result exceeds the maximum value that can be represented due to the restricted exponent range. It is not signaled when one of the operands is infinity, because infinity arithmetic is always exact.

Figure 2. Ranges of overflow and underflow for single-precision floating-point numbers

#### Rounding modes

Precision is not infinite and sometimes rounding a result is necessary. To increase the precision of the result and to enable round-to-nearest-even rounding mode, three bits are added internally and temporally to the actual fraction: *guard*, *round*, and *sticky* bit. While guard and round bits are normal storage holders, the sticky bit is turned '1' whenever a '1' is shifted out of range.

As an example we take a 5-bit binary number: 1.1001. If we left-shift the number four positions, the number will be 0.0001, no rounding is possible and the result will not be accurate. Now, let's say we add the three extra bits. After left-shifting the number four positions, the number will be 0.0001 101 (remember, the last bit is '1' because a '1' was shifted out). If we round it back to 5-bits it will yield: 0.0010, giving a more accurate result.

The four specified rounding modes are:

- 1. Round to nearest even: This is the default rounding mode. The value is rounded to the nearest representable number. If the value is exactly halfway between two infinitely precise results or between two representable numbers, then it is rounded to the nearest infinitely precise even number. For example, in one digit base-10 floating-point arithmetic, 3.4 will be rounded to 3, 5.6 to 6, 3.5 to 4 and 2.5 to 2.

- 2. Round to zero: In this mode, the excess bits will simply get truncated. For example, in two digit base-10 floating-point arithmetic, 3.47 will be truncated to 3.4, and -3.47 will be rounded to -3.4.

- 3. Round up: In round up mode, a number will be rounded towards  $+\infty$ . For example, 3.2 will be rounded to 4, while -3.2 to -3.

- 4. Round down: The opposite of round-up, a number will be rounded towards  $-\infty$ . For example, 3.2 will be rounded to 3 while -3.2 to -4.

### 2.2. IEEE 754 Floating-point Arithmetic

The IEEE 754 standard apart from specifying the representation format, the rounding modes and the exceptions also defines the basic operations that can be performed on floating-point numbers.

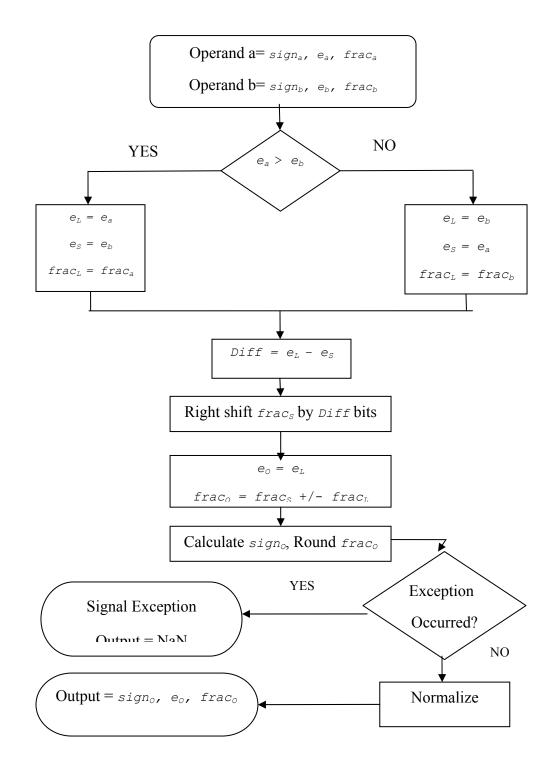

The Floating-point addition requires the following steps:

- 1. Aligning the mantissa's to make the exponent of the two operands equal and calculating the sign based on two operands. This exponent becomes the output exponent unless it is changed in the Step 3.

- 2. The mantissa bits are added or subtracted depending on the signs of the operands.

- 3. The result from the addition has to be rounded and normalized in order to represent it correctly within the IEEE 754 floating-point format. These three steps are implemented in the floating-point unit three pipeline stages labeled prenormalization, addition unit and postnormalization. The three stages are explained in detail in Chapter 3. Subtraction is the same as addition except that the sign of the subtrahend is inverted before adding the two operands.

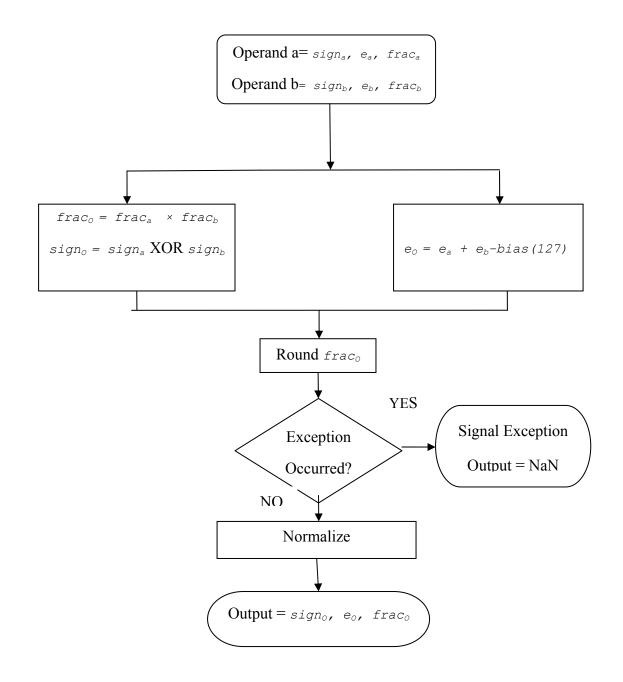

Floating-point multiplication also involves three steps:

- Prenormalization: Multiplication does not require alignment of mantissa in order to make the exponents of the operands equal. In multiplication, the exponents are added and the mantissa bits are transferred to the multiplication stage. The sign of the product is also calculated in this stage.

- 2. Multiplication: In this stage, the mantissa bits are multiplied using a multiplication algorithm. The product has twice as many mantissa bits as the multiplicands.

- 3. Postnormalization: The result from the multiplication is rounded and normalized to represent in the given precision format while updating the output exponent when required.

Figure 3 shows the basic algorithm for addition or subtraction of two floating-point numbers.

Figure 3. Basic floating-point addition algorithm

Consider a simple example for addition of two floating-point numbers:

Let's say we want to add two binary FP numbers with 5-bit mantissas:

A = 0|00000100|1001sign<sub>a</sub>=0; e<sub>a</sub>=00000100; frac<sub>a</sub>=1001 B = 0|00000010|0010

$sign_b = 0; e_b = 00000010; frac_b = 0100$

1. Get the number with the larger exponent and subtract it from the smaller exponent.

$e_L = 4, e_S = 2$ , so diff = 4 - 2 = 2.

2. Shift the fraction with the smaller exponent *diff* positions to the right. We can now leave out the exponent since they are both equal.

This gives us the following:  $1.1001\ 000 + 0.0100\ 100$

- 3. Add both fractions

- 1.1001 000 + 0.0100 100 -----1.1101 100

- 4. Round to nearest even gives us 1.1110.

- 5. Result = 0|00000100|1110.

------

The basic algorithm for floating-point multiplication is shown in Figure 4.

Figure 4. Basic Floating-point multiplication algorithm

Multiplication Example:

1. A = 001001001

$sign_a = 0; e_a = 01100100; frac_a = 1001$

B = 000100010

$sign_b = 0; e_b = 01101110; frac_b = 0100$

2. 100 and 110 are the stored exponents; logical exponents are obtained by subtracting the bias of 127 from them.

That is, the logical exponents in this case are 100-127 and 110-127.

3. Multiply the fractions and calculate the

1.1001 × 1.0010 ..... 1.11000010 ..... So frac<sub>o</sub>= 1.11000010 and

Output exponent: stored exponent = 100+110 and logical exponent = 100+110-127= 83

$e_{0} = 83$

- 4. Round the fraction to nearest-even:  $frac_0 = 1.1100$

- 5. Result: 0|11010010|1100

#### 2.3. History of Double-Double Arithmetic

Using single-length floating point arithmetic to describe or represent multi-length floating point arithmetic has been discussed and algorithms based on this approach were described by T.J.Dekker in his research report [3]. The report represents a double length floating point number as sum of two single length floating point numbers, one of them being negligible in single length precision. It also discusses the algorithms for basic operations like addition, subtraction and multiplication in the ALGOL 60 language. The Fortran-90 double-double precision system developed by D.H.Bailey uses two 64-bit IEEE arithmetic values to represent quad-precision values in the Fortran 90 programming language [4]. "Implementation of float-float operators on graphics hardware" discusses the methods for improving of precision in floating-point arithmetic on GPUs. The paper discusses different algorithms by Dekker, Knuth and Sterbenz, and the results, performance, and accuracy of these methods [7]. It describes the framework for software emulation of float-float operators with 44 bits of accuracy and proves that these high-precision operators are fast enough to be used in real-time multi pass algorithms [7]. The residual register algorithms discussed by Dieter and Dietz [23] and this thesis can be used with these or other precision extending algorithms.

Native-pair arithmetic is a more general term for double-double encompassing precisions other than double. As with double-double, it uses an extra floating-point number to represent error residual term resulting from a floating-point operation. A native-pair value does not have exactly double the precision of the single native value due the occurrence of zeroes in between the two mantissas. These zeroes make the precision equal to the number of bits in the two mantissas plus the number of zeroes between the mantissas [23]. In this approach, a higher-accuracy value is spread across the mantissas of two native floating-point numbers and the exponent of the lower component is used to align the mantissas [23]. The high component, called hi, takes the top most significant bits and those that are left, also referred to as residual are represented using the low component, called 10. The exponent of 10 will be less than that of exponent of hi by a minimum of N<sub>m</sub>, where N<sub>m</sub> is the number of mantissa bits in the native floating-point number. This means that if a higher precision value is spread over multiple native floating-point values, the exponents of consecutive 10 components keep decreasing by N<sub>m</sub>[1].

When considering a pair of native floating-point numbers and a 32-bit native mantissa being spread across them, the pair will have twice the precision of the mantissa being spread only if the exponent of the hi is at least  $N_m$  greater than that of the native bottom of the exponent range [1]. That is the dynamic range of the exponent is reduced by  $N_m$ steps or 10 percent. In a single-precision or 32-bit floating point system, the precision is limited by the exponent range to less than 11 float values [1]. Also, when there are zeros in the top of the lower-half of the higher precision mantissa, then the exponent of 10 part is further reduced by the number of zeros and the zeros are absorbed [2]. And if there are *K* zeros at the top of the lower-half then, the exponent of 10 part is reduced by *K*. This has certain implications which are as follows:

- Some values requiring up to *K* bits more precision than twice the native mantissa can be represented precisely, as the *K* zeros that come between the top half and the lower-half are absorbed [1].

- If the adopted native floating-point does not represent denormalized numbers, the Low component may fall out of range sometimes. For example, if the High exponent was 24 above the minimum value and number of zeros K = 1, then the result has 25 bits only and not 48 bits as the stored exponent of Low would have to be -1, which is not representable in IEEE format [1].

#### 2.4. The Residual Register

Native-pair arithmetic involves computing the error residual term from the floating point operation and using it to perform further computations. This error residual computation is the major overhead in the native-pair arithmetic. Dieter and Dietz proposed adding a residual register to save this left over information [23]. The residual register is only used to store the mantissa bits, exponent bits, the sign bit, and a complement flag. The value stored in the register need not be normalized immediately and has  $N_m + 2$  mantissa bits with an implicit leading 1 bit. The same normalization hardware used for floating-point operations normalizes the residual value only when it is being moved into an architectural register. The complement flag indicates whether the residual value must be complemented before moving into the architectural register. Normalizing the residual register is done by giving a "MOVRR" instruction that copies the residual register value

into an architectural register after normalizing it into IEEE 754 format. Also each operation results in updating the residual register with a new error residual value.

| Sign  | Complement Flag | Exponent   | Mantissa    |

|-------|-----------------|------------|-------------|

| 1 bit | 1 bit           | ← 8 bits → | ← 25 bits → |

#### Figure 5. Residual register

Consider two floating-point numbers x, y and o be an operation such as +, -, or ×. Let sign(x), exp(x) and mant(x), respectively denote the sign, exponent and mantissa of x.  $Fl(x \circ y)$  denotes the primary result of a floating-point operation and  $Res(x \circ y)$  be the residual of the floating-point operation. For operations discussed here namely addition, subtraction and multiplication the primary result and the residual are related as  $x \circ y = Fl(x \circ y) + Res(x \circ y)$ . This property holds true only for the round to nearest mode when IEEE 754 format is used. Depending on which rounding mode is used, the sign of the residual register value is set accordingly [23]. The residual logic only needs the information if the primary result is rounded up or down. Depending on this information the sign and the complement flag of the residual register is set as follows:

- When  $Fl(x \circ y) = x \circ y$ , the primary result is correct and the residual value is zero.

- When F1 (x o y) < x o y, the primary result p has been rounded down to the floating-point value with next lower magnitude. The residual r then takes the same sign as p to make x o y = F1 (x o y) + Res (x o y).</li>

- When F1 (x o y) > x o y, the primary result F1 (x o y) is rounded up to the next larger magnitude value. The residual r then takes the opposite sign as F1 (x o y) to make x o y = F1 (x o y) Res (x o y).

#### 2.5. Native-pair Addition and Subtraction

Addition or subtraction of two floating-point numbers 'a' and 'b' with 'b' being the smaller of the two, involves the shifting of the smaller number to align its radix point with that of the larger number. When the signs of the two numbers are the same, the numbers are added whereas in the case of opposite signs, the numbers are subtracted. The mantissa bits in the smaller number with significance less than  $2^{\exp(a) - (N_m + 1)}$  are stored in the residual register with least significant bit in the rightmost position, and the exponent is set to exp(b) when  $exp(a) - exp(b) \ge N_m + 1$  and the complement flag is not set. When  $exp(a) - exp(b) < N_m + 1$  or the complement flag is set, the residual register gets the bits in b with significance ranging from  $exp(a) - N_m + 1$  down to  $exp(a) - 2(N_m + 1)$ . That is, the residual register value is just below the primary output value. In this case, the exponent is set to  $exp(a) - 2(N_m + 1)$  with the radix point assumed to be to the right of the least significant residual register bit. The sign and complement flag are set depending on the signs of 'a' and 'b', and whether result p is rounded up or down. Four cases that arise depend on the signs of 'a', 'b' and whether the primary result is rounded up or down, are shown in Table 3 below:

| Case   | Sign of <i>a</i> | Sign of b | Rounded   | Complement | Sign of Residual    |

|--------|------------------|-----------|-----------|------------|---------------------|

|        |                  |           | up / down | flag       | register: Sign(rr)  |

| Case 1 | Sign(a)          | Sign(a)   | Down      | Cleared    | Sign(a)             |

| Case 2 | Sign(a)          | Sign(a)   | Up        | Set        | Opposite of sign(a) |

| Case 3 | Sign(a)          | -Sign(a)  | Down      | Set        | Sign(a)             |

| Case 4 | Sign(a)          | -Sign(a)  | Up        | Cleared    | Opposite of Sign(a) |

Table 3. Different cases for sign and complement flag of residual register

#### Native-pair Arithmetic Addition Algorithms

The algorithms that are discussed here are native-pair arithmetic algorithms for normalizing and adding two native-pair numbers. Each algorithm can be implemented with and without using the residual register. Algorithm 1 shows the nativepair\_normalize function adds two native floatingpoint numbers to produce a native-pair result. Given an unnormalized high and low pair of native numbers, the normalized native-pair is computed using this function. In general, the normalized native-pair is created without using the residual register.

# Algorithm 1. Native-pair normalization algorithm without using the residual register:

```

nativepair nativepair_normalize(native hi, native lo)

{

nativepair r;

native hierr;

r.hi = hi + lo;

hierr = hi - r.hi;

r.lo = hierr + lo;

return (r);

}

```

Algorithm 2 shows the use of the residual register in the nativepair\_normalize function. The hierr variable denotes the error residual computed from hi component. The getrr () function is assumed to be an inline function that returns the residual register value using a single MOVRR instruction. Compared to the Algorithm 1, Algorithm 2 does not need to compute hierr and as a result, the number of instructions is reduced by one relative to Algorithm 1. Every basic operation ends by normalizing the result so this reduction decreases the instruction count for every native-pair operation.

#### Algorithm 2. Native-pair normalization algorithm using the residual register:

```

nativepair nativepair_normalize (native hi, native lo)

{

```

```

nativepair r;

```

```

r.hi = hi + lo;

r.lo = getrr ();

return (r);

```

Algorithm 3 describes the addition of b (native floating point number) to a (native-pair number). The algorithm adds b to hi component of a, computing the residual result and adding the residual result to lo component. It then normalizes the final result.

# Algorithm 3. Addition of Native-pair number and a native number without residual register hardware.

```

nativepair nativepair_native_add (nativepair a, native b)

{

native hi = a.hi + b ;

native bhi = hi - a.hi;

native ahi = hi - bhi;

native bhierr = b - bhi;

native ahierr = a.hi - ahi;

native hierr = bhierr + ahierr;

native lo = a.lo + hierr;

return (nativepair_normalize(hi,lo));

}

```

Algorithm 4 describes the same native-pair and native number addition with the use of residual register. This usage computes the hierr component using the getrr () inline function and so eliminates the use of ahierr, bhierr i.e., instructions to compute ahi, bhi, ahierr, bhierr. As a result, number of instructions is reduced by four when with respect to Algorithm 3 which does not use residual register.

Algorithm 4. Addition of Native-pair number and a native number with residual register hardware.

```

nativepair nativepair_native_add (nativepair a, native b)

{

native hi = a.hi + b;

native hierr = getrr();

native lo = a.lo + hierr;

return (nativepair_normalize(hi,lo));

}

```

Algorithm 5 shows addition of two native-pair numbers without using the residual register and Algorithm 6 adds two native-pair numbers using the residual register. In Algorithm 5, which shows addition without residual register, the residual from adding the two high components is stored in ahierr or bhierr depending on the values of a and b. When a > b, bhierr contains the residual and ahierr is zero and when b > a, ahierr contains the residual and bhierr is zero. Such a system of computing is faster than using a condition to decide which one to compute. The addition algorithm with residual register reduces the instruction count to 6 compared to Algorithm 5 which takes 11 instructions.

# Algorithm 5. Addition of two Native-pair numbers without residual register hardware.

```

nativepair nativepair_add (nativepair a, nativepair b)

{

native hi = a.hi + b.hi;

native lo = a.lo + b.lo;

native bhi = hi - a.hi;

native ahi = hi - bhi;

native bhierr = b.hi - bhi;

```

```

native ahierr = a.hi - ahi;

native hierr = bhierr + ahierr;

lo = lo + hierr;

return (nativepair_normalize(hi,lo));

}

```

Algorithm 6. Addition of two Native-pair numbers with residual register hardware.

```

nativepair nativepair_add (nativepair a, nativepair b)

{

native hi = a.hi + b.hi;

native hierr = getrr();

native lo = a.lo + b.lo;

lo = lo + hierr;

return (nativepair_normalize(hi,lo));

}

```

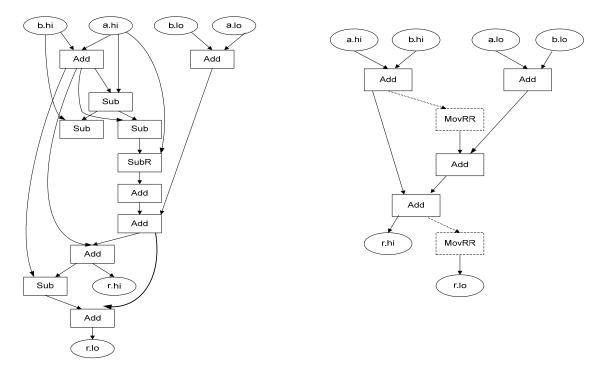

Figure 6 shows the dataflow of the native-pair addition algorithm with and without residual register. Each ADD or SUB instruction typically would have a latency of 4 clock cycles. The MOVRR instruction is assumed to have a latency of 2 clock cycles as a worst case. Native-pair addition without residual register requires 9 instructions in its critical path and with a latency of  $36 = 9 \times 4$  clock cycles. Addition with residual register requires 3 ADD/SUB instructions and 2 MOVRR instructions yielding to a total latency of  $16 = 3 \times 4 + 2 \times 2$  clock cycles. But this latency can be decreased without changing the critical path by delaying lo portions of an input to the algorithm in the dataflow. This reduces the latency to 28 = 36-8 cycles in native-pair addition without residual register and 14 = 16-2 cycles in the native-pair addition with residual register. This results in exactly  $2 \times$  speedup over the algorithm not using residual register [23].

Figure 6. Native-pair addition data flow, conventional and residual algorithms.

## 2.6. Native-pair Multiplication

In multiplication of two floating-point numbers as opposed to addition, there is no shifting of the mantissa bits in order to make the exponents of the two numbers equal. Multiplication of two n-bit mantissa numbers produces a 2n-bit result and the exponents of the two numbers are simply added. The lower n-bits of the 2n-bit result are put into the residual register and its exponent is set to  $exp(a) - (N_m+1)$ . When the result is rounded down, the sign of the residual register is same as that of the result and the complement flag is cleared. On the other hand when the result is rounded up, the sign is set opposite to the sign of the result and the complement flag is set.

| Case   | Sign of | Rounded up / down | Complement Sign of Residual |                     |

|--------|---------|-------------------|-----------------------------|---------------------|

|        | product |                   | flag                        | register : Sign(rr) |

| Case 1 | Sign(p) | Down              | Cleared                     | Sign(p)             |

| Case 2 | Sign(p) | Up                | Set                         | Opposite of Sign(a) |

Table 4. Cases for complement flags and signs of residual register

#### Multiplication algorithms for native-pair multiplication

Algorithm 7 shows the multiplication of two native-pair numbers a and b without residual register hardware. The algorithm uses a native\_mul function to multiply two high components of the two native-pair numbers. The multiplication of the high and low components also takes place producing three low components namely native\_mul result low component, a.hi × b.lo and b.hi × a.lo. The fourth term, a.hi × b.lo, is too small to have an influence on the result. All the three low components are added to produce the final low component of the result. The native\_mul function implementation is simplified if the processor has a fused multiply- subtract instruction that preserves the full precision of the product before addition. In such a case the residual value can be obtained by subtracting the rounded product from the full precision product. When such a provision is unavailable the native\_mul function requires the entire component-wise multiplication of the high and low components.

#### Algorithm 7. Native-pair multiplication without residual register hardware

```

nativepair nativepair_mul (nativepair a, nativepair b)

{

nativepair tops = native_mul (a.hi, b.hi);

native hiloa = a.hi * b.lo;

native hilob = b.hi * a.lo;

native hilo = hiloa + hilob;

tops.lo = tops.lo + hilo;

return (nativepair_normalize (tops.hi, tops.lo));

}

```

#### Algorithm 7.1. native\_mul function

```

#define NATIVEBITS 24

#define NATIVESPLIT ((1<<(NATIVEBITS - (NATIVEBITS/2))) +

1.0)</pre>

```

```

nativepair native mul (native a, native b)

{

nativepair c;

#ifdef HAS FUSED MULSUB

c.hi = a * b;

c.lo = a * b - c.hi;

#else

native asplit = a * NATIVESPLIT;

native bsplit = b * NATIVESPLIT;

native as = a - asplit;

native bs = b - bsplit;

native atop = as + asplit;

native btop = b + bsplit;

native abot = a - atop;

native bbot = b - btop;

native top = atop * btop;

native mida = atop * bbot;

native midb = btop * abot;

native mid = mida+ midb;

native bot = abot * bbot;

c = nativepair normalize (top, mid);

c.lo = c.lo + bot;

#end if

return(c) ;

}

```

When fused multiply-add is not available the residual register hardware simplifies the native\_mul function from 17 instructions to two instructions. The Algorithm 8 shown below takes 8 instructions to perform the multiplication. Though the instruction count is

the same as the fused multiply-add implementation, the need for a wider adder is removed in the residual register implementation.

#### Algorithm 8. Native-pair multiplication using residual register hardware

```

nativepair nativepair_mul (nativepair a, nativepair b)

{

nativepair tophi = a.hi * b.hi;

native toplo = getrr ( );

native hiloa = a.hi * b.lo;

native hilob = b.hi * a.lo;

native hilo = hiloa + hilob;

tops.lo = toplo + hilo;

return (nativepair_normalize (tophi, toplo));

}

```

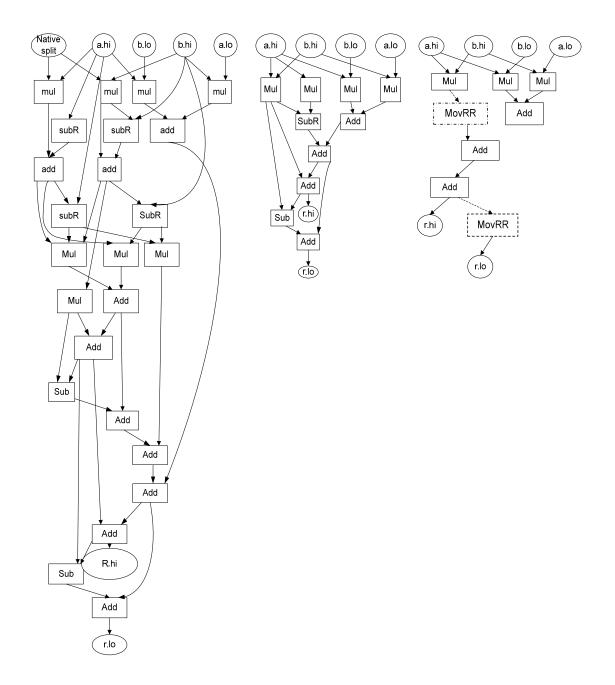

Nativepair multiplication has three data flow graphs: conventional, fused multiply-add and residual register implementation which are shown in Figure 7 in the next page. Depending on the latency of add and subtract operations in the critical path, the speed up resulting from the fused multiply-add implementation is 2.3 and that resulting from residual register implementation is 3 [23]. The residual register implementation also has an added advantage that the critical path can be implemented with only a 2-stage pipeline with careful instruction scheduling. Such improvisation is not possible in conventional and fused multiply-add implementations as they suffer from greater need for a larger pipeline [23].

Figure 7. Native-pair multiplication data flow, conventional and residual algorithms

#### Chapter 3. Native-pair Floating-point Unit

This chapter describes the working of the native floating-point unit addition/subtraction and multiplication units, followed by the construction of the native-pair floating-point unit and usage of the residual register hardware.

#### 3.1. Native Floating-Point Addition/Subtraction

The native floating-point addition/subtraction is subdivided into three steps: prenormalization, addition or subtraction and postnormalization.

#### 3.1.1. Prenormalization

The input operands to the floating-point unit first go to the prenormalization unit. This unit finds the difference between the exponents of the two operands, shift the mantissa with lower exponent to make the two exponents equal and send the mantissa bits and the exponent o the addition stage.

Initially the two operands A and B are divided into sign, exponent and mantissa fields. After the last step the following fields or signals are obtained:

- Exp (A)

- Exp (B)

- Mant(A)

- Mant(B)

The exp (A) and exp (B) of all the input operands are checked for zero values to see if they are denormalized. If an operand is denormalized, its exponent is incremented by 1 to make the exponent equal to -126 after unbiasing. If exp(A) and exp(B) are non-zero values ,the corresponding operands are considered normalized. The fraction values are concatenated with 5 more bits – carry, hidden, guard, round and sticky bits. Carry and hidden bits are added as most significant bits. Initially the carry bit is 0 and the hidden bit is 0 if the operand is denormalized otherwise the hidden bit is 1. The guard, round and sticky bits are appended at the end of the fraction bits and are initially all zeroes. After this step fractions take the form of

- New Mant(B) = carry, hidden, mant(B), guard, round, sticky.

- New Mant(B) = carry, hidden, mant(B), guard, round, sticky.

A comparator COMP1 is used to check which exponent is greater and a multiplexer MUX1 is used to assign the greater exponent to the output exponent based on the comparator output signal. Multiplexer MUX2 is used to give the difference of the two exponents. If exp(A) > exp(B), then MUX2 gives the difference exp(A) - exp(B) if not it gives the difference exp(B) - exp(A). The fraction bits of the lower exponent operand's mantissa are shifted right as many bits as the difference obtained from the exponent difference. The sticky bit for the shifted mantissa is computed and updated. The two updated mantissas with the output exponent and other signals are sent to the next stage. Figure 8 shows the prenormalization process.

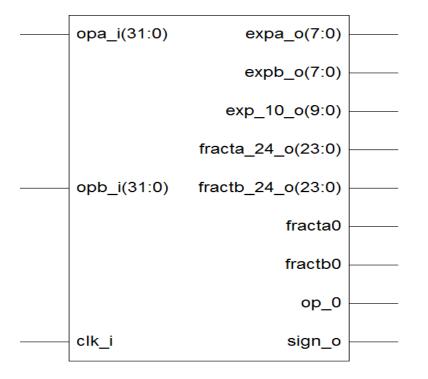

Figure 8. Prenormalization unit for Floating-point addition

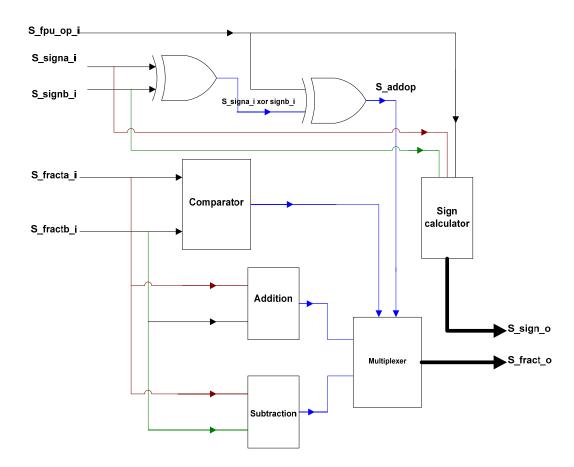

#### 3.1.2. Addition/Subtraction Stage

This stage has a simple functionality of computing the sign of the output and performing the addition or subtraction of mantissas based on the sign of the operands. The two mantissas are compared and the operation i.e., addition or subtraction to be performed is computed based on which mantissa is greater, signs of the two operands A and B and the opcode. Table 5 shows the different cases that arise. A and B having same signs with an opcode of 0, indicating addition is performed. If the opcode is a 1 then subtraction is performed. On the other hand A and B having opposite signs, for opcode of 0, subtraction is performed and for opcode of 1 addition is done.

Figure 9. Addition unit for Floating-point addition

The sign of the output is computed based on the signs of the operands A and B, which mantissa is greater and the operation being performed. If the operation is an addition then the two mantissas are added and if it is a subtraction then the lower mantissa is subtracted from the higher mantissa. The output sign and mantissa are sent to the postnormalization

stage along with input operands passed by the prenormalization stage. Input operands are required in postnormalization for generation of exceptions.

| Opcode | Sign of A | Sign of B | Operation   |

|--------|-----------|-----------|-------------|

| 0      | sign      | sign      | Addition    |

| 0      | sign      | ~ sign    | Subtraction |

| 1      | sign      | sign      | Subtraction |

| 1      | sign      | ~sign     | Addition    |

Table 5. Addition or subtraction cases based on opcode and signs of the operands

## 3.1.3. Postnormalization

Postnormalization is the final stage of any floating-point operation. The inputs to this stage are the addition/subtraction unit output, the output exponent, the output sign and the rounding mode.

The postnormalization unit checks the result of the addition/subtraction stage for a carry. If the carry bit in the result is set then, shift the result right once and increase the output exponent by one. If the result has the hidden bit equal to zero then, the result must be left shifted until the hidden bit is one. To determine how far to shift the mantissa, the number of zeros starting from the most significant bit is counted. After the shift is performed, the exponent is decreased by the same number. Once again the sticky bit is checked to find if any bits were lost. Depending on the rounding mode and the sticky bits at different stages in the postnormalization, the result is rounded up or rounded down. The carry bit is checked again to see if carry occurred and if carry has occurred then the result is shift right once and the exponent is incremented by one. Finally, the result is checked for exceptions such as NaN, infinite, overflow, inexact result and depending on these values, the final result along with the exception flags are send to the output. The postnormalization unit is shown in Figure 10.

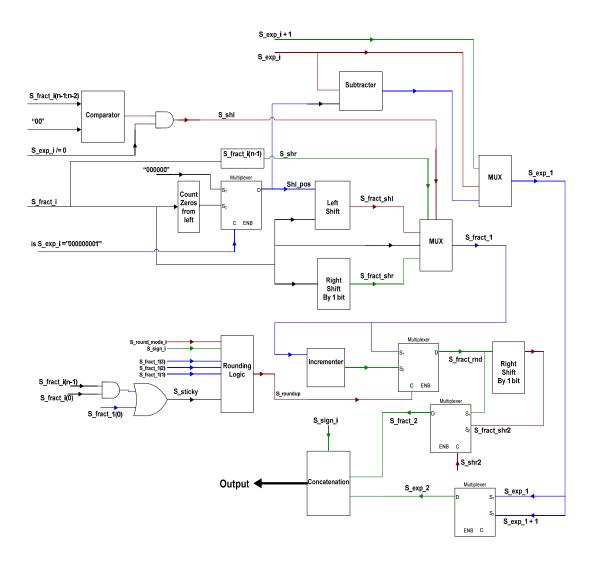

## Figure 10. Postnormalization unit for Floating-point addition.

#### 3.2. Native Floating-Point Multiplication

The native floating-point multiplication unit is also subdivided into three steps: prenormalization, multiplication and postnormalization.

#### 3.2.1. Prenormalization

The input operands to the multiplication unit first go through the prenormalization unit. As compared to prenormalization in addition, the prenormalization in multiplication has less functionality. This unit checks if the operands A and B are denormalized, adds the exponents of A and B and transfers the mantissas to the multiplication stage.

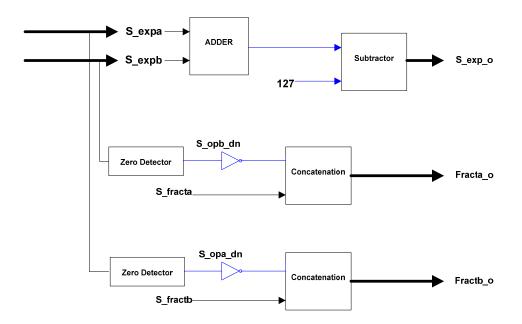

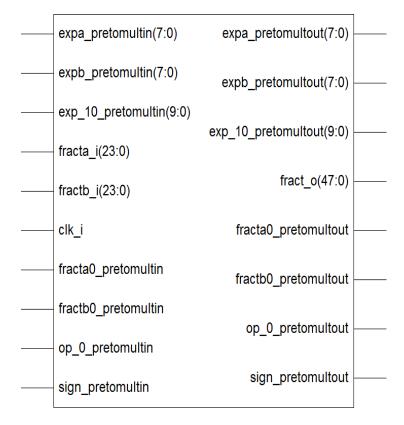

Figure 11. Prenormalization unit in floating-point multiplication.

Initially the two operands A and B are divided into sign, exponent and mantissa fields. After the last step the following fields or signals are obtained:

- Exp(A)

- Exp(B)

- Mant(A)

- Mant(B)

The exp (A) and exp (B) of the all the incoming operands are checked for zero values to see if they are denormalized. If an operand is denormalized, its exponent is incremented by 1 to make the exponent equal to -126 after unbiasing. The fraction values are appended with just 1 more bit, the hidden bit as the most significant bit. The hidden bit is 0 if the operand is denormalized otherwise the hidden bit is 1. After this step fractions take the form of

- New Mant(B) = hidden, mant(B)

- New Mant(B) = hidden, mant(B)

The exponents are added, but since the exponents are already biased i.e., we are baising the exponent twice and so 127 is subtracted from the sum. The two updated mantissas with the output exponent and other signals are sent to the next stage.

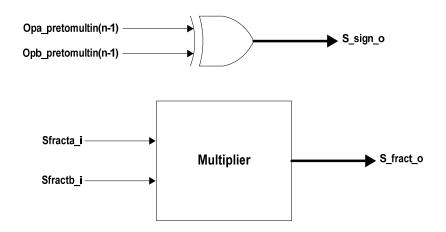

#### 3.2.2. Multiplication Stage

This stage is used to multiply the two mantissas obtained from the previous stage. The multiplier used is a Booth's parallel multiplier model. An exclusive-or gate is used to obtain the sign of the product. The output sign s\_sign\_o as well as the product s\_fract\_o are transferred along with the other signals to the postnormalization stage.

Figure 12. Multiplication unit for Floating-point multiplication

#### 3.2.3. Postnormalization

The inputs to this stage are the multiplication unit output, the prenormalization exponent output, the multiplication sign output and the rounding mode. The postnormalization stage checks the multiplication output for a carry. If a carry has occurred, the multiplication output is shifted right once to normalize it. If the result has the hidden bit equal to zero then, the result must be left shifted until the hidden bit is one. For this, the number of zeros starting from the most significant bit is counted. After the shift is performed, the exponent is decreased by the same number. Once again the sticky bit is checked to find if any bits were lost. Depending on the rounding mode and the sticky bits at different stages in the postnormalization, the result is rounded up or rounded down. The carry bit is checked again to see if a carry occurred. If a carry has occurred then the result is shift right once and the exponent is incremented by one. Finally, the result is checked for exceptions such as NaN, infinite, overflow, inexact result and depending on these values, the final result along with the exception flags are send to the output.

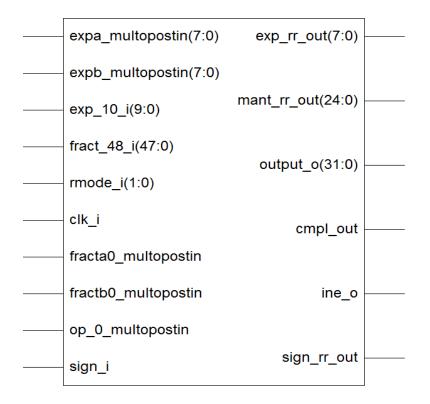

Figure 13. Postnormalization unit for Floating-point multiplication

#### 3.3. Native-pair Floating-point Addition/subtraction

Native floating-point addition/subtraction has been discussed in Section 3.1.1. This section discusses the 32-bit native-pair floating-point addition/subtraction and the extra hardware added to the native floating-point addition/subtraction unit to make it work as a native-pair floating-point addition/subtraction unit. Native-pair addition/subtraction also

is subdivided into three steps: prenormalization, addition or subtraction and postnormalization. Each step and its hardware addition are discussed in detail below.

# 3.3.1. Prenormalization

The native-pair prenormalization unit, apart from doing the normal operation of making the exponents equal and aligning the mantissa's, also includes the first of the residual register operations.

For a better understanding the steps of the native normalization are again repeated. Initially the two operands A and B are divided into sign, exponent and mantissa fields. After the last step the following fields or signals are obtained:

- Exp(A)

- Exp(B)

- Mant(A)

#### • Mant(B)

The exponents  $\exp(A)$  and  $\exp(B)$  of all the input operands are checked for zero values to see if they are denormalized. The exponent is incremented by 1 to make the exponent equal to -126 after unbiasing. The fraction values are concatenated with 5 more bits – carry, hidden, guard, round and sticky bits. Carry and hidden bits are added as most significant bits. Initially the carry bit is 0 and the hidden bit is 0 if the operand is denormalized else hidden bit is 1. The guard, round and sticky bits are appended at the end of the fraction bits and are initially all zeroes. After this step fractions take the form of

- New Mant(B) = carry, hidden, mant(B), guard, round, sticky.

- New Mant(B) = carry, hidden, mant(B), guard, round, sticky.

A comparator COMP1 is used to check which exponent is greater and a multiplexer MUX1 is used to assign the greater exponent to the output exponent based on the comparator output signal. Multiplexer MUX2 is used to give the difference of the two exponents. If exp(A) > exp(B), then MUX2 gives the difference exp(A) - exp(B) if not it gives the difference exp(B) - exp(A). An 'and signal' is generated which is a 25 bit signal consisting of zeroes and ones in till the position of the exponent difference (s exp diff-1) i.e. if the exponent difference is 4 then the and signal is "0000000000000000000001111". The fraction bits of the lower exponent operand's mantissa's fract small are shifted right as many bits as the difference obtained from the exponent difference. A bit-wise AND operation is performed between the smaller mantissa s fract small and the and signal, the result is the initial mantissa part for the residual register. The bits that are being shifted out are stored in the mantissa of the residual register. The exponent of the residual register is set to the exponent of the lower mantissa. The sticky bit for the shifted mantissa is computed and updated. One other signal that is generated here is exp greater 24 which indicates if the exponent difference is greater than 24. The two updated mantissas with the output exponent, residual register exponent, mantissa and other signals are sent to the next stage.

#### 3.3.2. Addition/subtraction Stage

There is no change in the functionality of the addition/subtraction unit. It takes in the mantissas and the operand signs as inputs. After logically generating which operation has to be performed, it performs that operation i.e., addition or subtraction. Output sign is generated based on the operation, the signs of the operands and which operand is greater. The operation output, the output sign and other inputs such as the residual register values from the prenormalization stage etc., are all passed to the postnormalization stage.

#### 3.3.3. Postnormalization

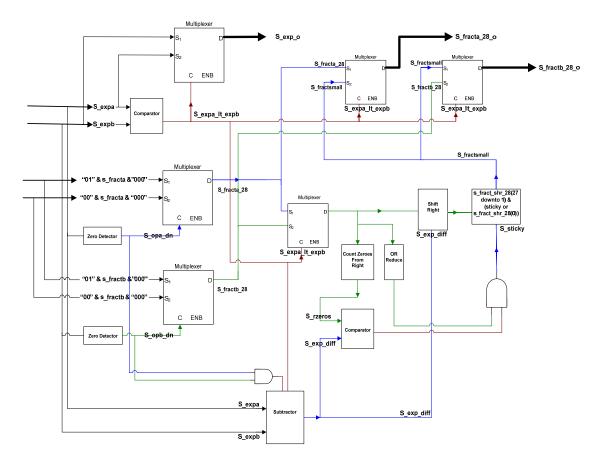

Postnormalization in the Section 3.3.3 involves all the main operation surrounding the residual register hardware operation. The inputs to this stage are the addition/subtraction unit output, prenormalization output exponent, addition unit output sign, rounding mode, residual register values from the prenormalization stage. The following are the steps involved in the postnormalization stage:

Check the result of the addition/subtraction stage for a carry. If carry bit in the result is set then, shift the result right by once and increase the output exponent by one. If the result has the hidden bit equal to zero then, the result must be left shifted until the hidden bit is one. For this, the number of zeros starting from the most significant bit is counted. After the shift is performed, the exponent is decreased by the same number.

As the result is shifted, one bit before the guard bit is lost and this bit has to be prepended to the residual register. This bit has to be prepended before the bits that were inserted in the prenormalization stage. For this purpose a decoder is used which whose output d1 has a value in the position which corresponds to the exponent difference. D1 is logically ANDed with the output of the addition/subtraction and then ORed with the mantissa from the prenormalization stage to get the new updated mantissa.

s\_mant\_rr2\_br <= ('0' & mant\_i\_rr2) or (d1 and s\_fract\_28\_i (27 downto 3));

Figure 15. Postnormalization unit for Native-pair addition with Residual register

Once again the sticky bit is checked to find if any bits were lost. Depending on the rounding mode and the sticky bits at different stages in the postnormalization, the result is rounded up or rounded down. The carry bit is checked again to see if carry occurred and if carry has occurred then the result is shift right once and the exponent is incremented by one.

As the result is shifted right again, one bit before the guard bit is lost and this bit has to be added to the residual register. This bit has to be added before the bit that was added after the right shift performed before rounding. For this purpose another decoder is used whose output D2 has a value '1' in the position which next to '1' in D1. D2 is logically ANDed with the output of the after the rounded result is shifted right and then ORed with the mantissa s\_mant\_rr2\_br to get the new updated mantissa.

s\_mant\_rr2\_ar <= ('0' & s\_mant\_rr2\_ar) or (d2 and s\_fract\_rnd (27 downto 3));

Suppose that the exponent difference in the prenormalization was greater than 24, and all the bits of the smaller mantissa are shifted into the residual register. Now in the postnormalization stage if the result was shifted right twice once before rounding and once after rounding, then 2 bits must be stuck on the So. In total the residual register mantissa temporarily can have 27 bits and then the 25 most significant bits are stored as final residual value.

The sign of the residual register and the complement flag are also generated in this stage. If the complement flag is set, then residual value is complemented before it is stored in an architectural register. The signal exp\_greater\_24 that was generated in the prenormalization stage to check if the exponential difference was greater than the number of mantissa bits + 1 is used here.

If the signal is set, then the exponent of the residual is set to higher exponent  $-2(N_m+1)$  else exponent is set to lower exponent, where  $N_m$  is the number of mantissa bits.

Finally, the result is checked for exceptions such as NaN, infinite, overflow, inexact result and depending on these values, the final result along with the exception flags are send to the output.

The next instruction is to normalize the residual register value which happens with the MOVRR signal going high. During this stage, residual register value is concatenated with the guard, round and the sticky bits in the end to make it 28 bits and this value is directly sent into the postnormalization input for normalization. This normalized residual register value is later used in computation related to native-pair algorithms.

#### 3.4. Native-pair Floating-point Multiplication

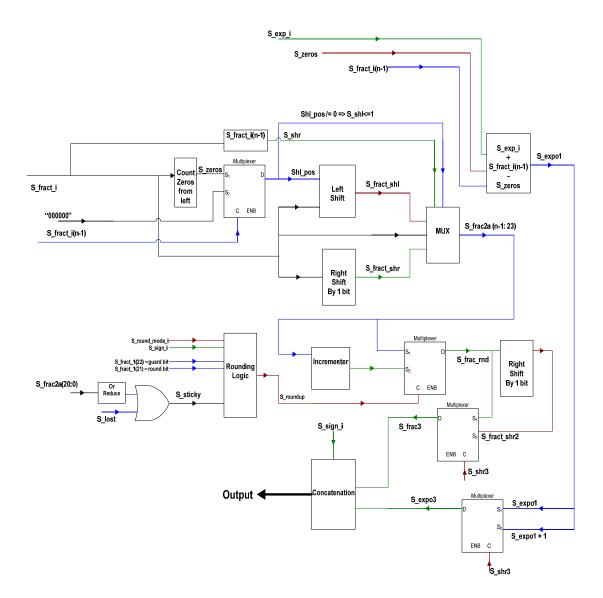

This section discusses the 32-bit native-pair floating-point multiplication and the extra hardware added to the native floating-point multiplication unit to make it work as a native-pair floating-point multiplication unit. The residual register hardware in a multiplication is less complex when compared to addition. Since there is no shifting of mantissas in multiplication, there is no residual register functionality in the prenormalization. So the entire residual register operation takes place only in the postnormalization stage. Hence only the changes and the steps involved to the postnormalization are discussed here.

## 3.4.1. Postnormalization

The inputs to this stage are the multiplication unit output, the prenormalization output exponent, the multiplication sign output and the rounding mode. The following are the steps involved in the native-pair multiplication postnormalization stage

# Figure 16. Postnormalization unit for Native-pair multiplication with Residual register

Check the result of the multiplication stage for a carry. If carry bit in the result is set then, shift the result right by once and increase the output exponent by one. In postnormalization, the 25 most significant bits are taken into consideration for the final output, hence initially the residual register consists of the 23 least significant bits.